Overview

The Digital Neurosynaptic Core is intended to leverage the density of VLSI to enable circuit-level simulation of neural networks. In short, each core consists of a sea of neurons which are interconnected with a reconfigurable event-based routing system. This routing network is capable of intra- as well as intra-chip communication for neural network scalability.

Details

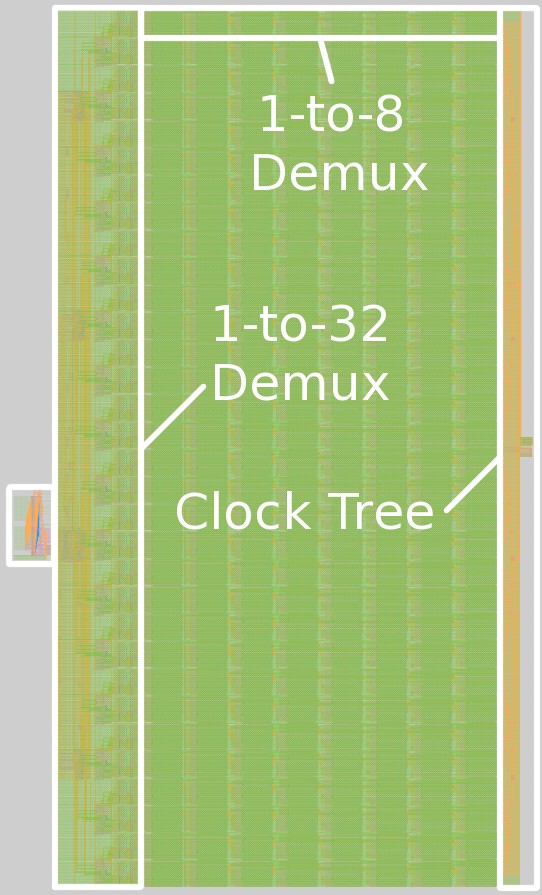

The routing network is time-multiplexed to allow multiple one-to-many event communications from single neurons to all downstream neurons. Part of this system is a scheduler, which essentially takes the form of a 1-to-1024 demultiplexer or "demux", as shown below.

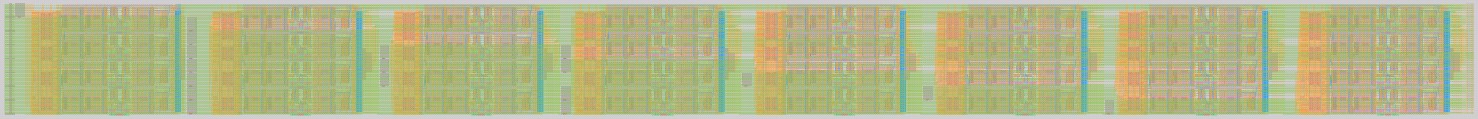

The highlighted portion on the very left denotes interface circuitry for the scheduler. Although the scheduler is asynchronous, the output interface of the demux shares its boundary with a synchronous system, so a flip-flop-based synchronizer and associated clock-tree are necessary. The bulk of the scheduler is made of 32 1-to-8 demux stages, each of which has 8 1-to-4 demux stages, shown below. A single output of the 1-to-32 demux feeds a "slice" of 8 1-to-4 demux stages.

My involvement in this project was in the VLSI layout of the demux stages, as well as the design and layout of the clock tree. Note the clock tree extends deep into each 1-to-8 demux, as the clock tree denoted in the scheduler figure only routes to each of the 32 1-to-8 demux slices. Filipp Akopyan led the scheduler project and was supported by the core team of myself, Benjamin Hill, Carlos Tadeo Ortega Otero, and Robert Karmazin.

Related Publications

-

Nabil Imam and Rajit Manohar. Address-Event Communication Using Token-Ring Mutual Exclusion. ASYNC 2011

-

Paul Merolla, et al. A Digital Neurosynaptic Core Using Embedded Crossbar Memory with 45pJ per Spike in 45nm. CICC 2011