Overview

The primary advantage to Asynchronous FPGAs is their pipelined interconnect, which can dramatically improve throughput. The original architecture was developed by John Teifel and Rajit Manohar at Cornell in 2003-04, and was extended with 3D integration in 2006.

Details

The 2010 revision, designed by Benjamin Hill, adds the following features:

-

Clustered Logic Blocks

-

Increased Routing Resources

-

Dynamic Partial Reconfiguration

-

Power Gating

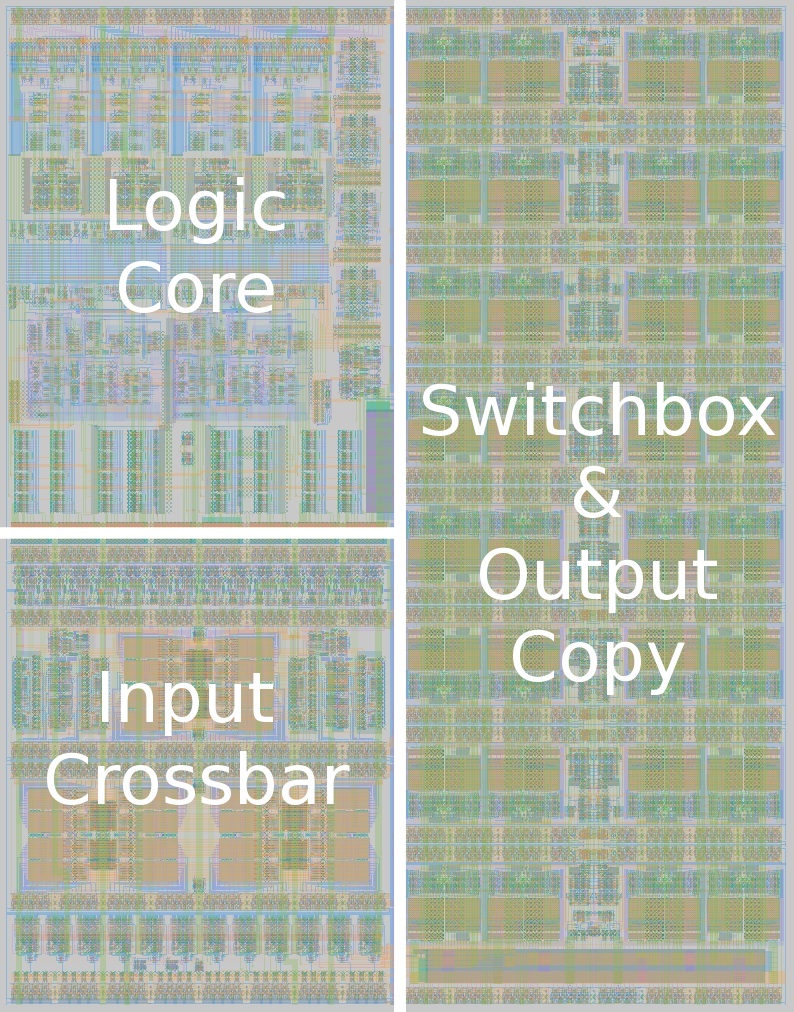

The FPGA tile floorplan can be seen above, measuring roughly 125um by 200um in a 65nm process. The Logic Core is made up of a cluster of four logic blocks, two full adder stages, and some I/O circuitry. It has its own power domain. Note that only the first four (of eight) levels of metallization are shown for readabilty. The remaining 75% of each FPGA tile is devoted to routing circuitry, either within the tile or between tiles.

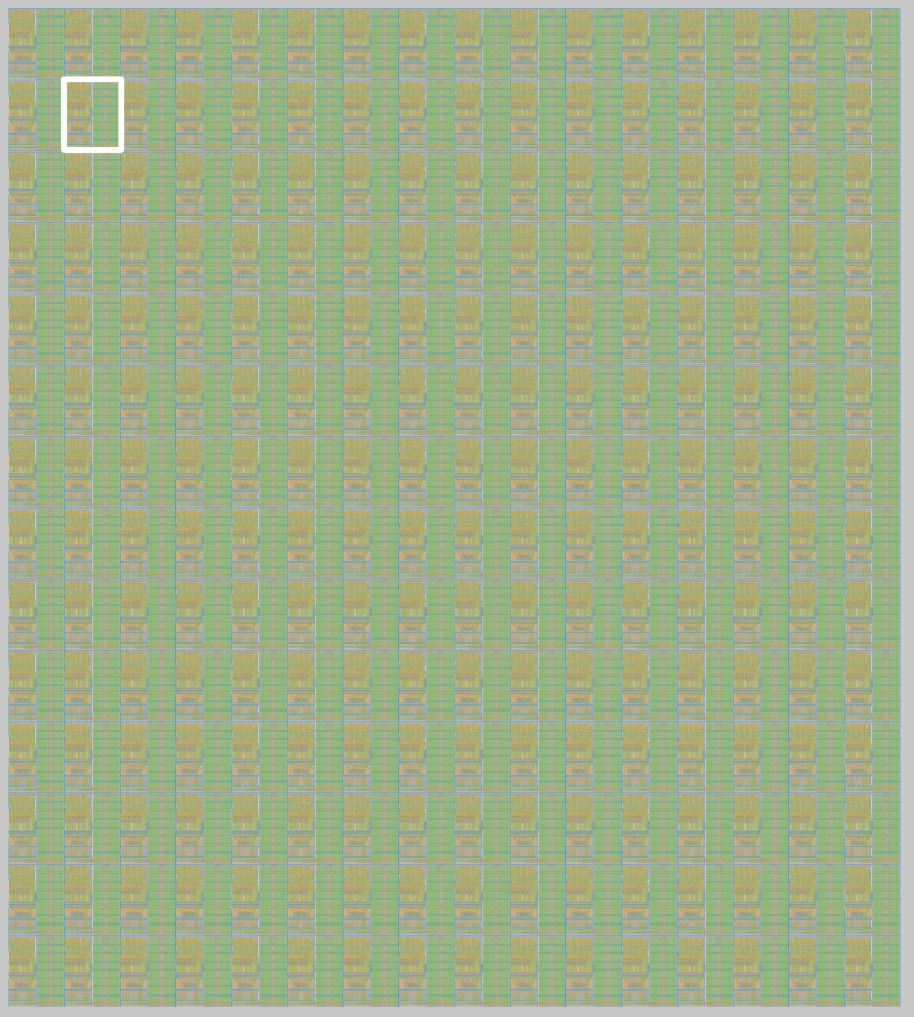

A single tile can be seen in the 16x14 tile fabric above. Again, only the first four levels of metallization are shown. There is no explicit global routing. All inter-tile routing is already done in each tile, so all tiles simply snap-together when arrayed. This is true of the global power routing as well, which was built with the secondary purpose of shielding data-carrying wires from crosstalk. The FPGA configuration memory has been implemented using local SRAM blocks, and each tile can be power gated independently down to the logic core level.

My involvement in this project was limited to a hand in designing the adder carry chain as well the full-custom VLSI layout of the logic core, sans the layout of the full adders. Core team members for the 2010 effort, lead by Benjamin Hill, were Robert Karmazin and Carlos Tadeo Ortega Otero.

Related Publications

-

John Teifel and Rajit Manohar. Programmable Asynchronous Pipeline Arrays. FPL 2003

-

John Teifel and Rajit Manohar. Highly Pipelined Asynchronous FPGAs. FPGA 2004

-

John Teifel and Rajit Manohar. An Asynchronous Dataflow FPGA Architecture. IEEE Transactions on Computers 2004

-

Song Peng, et al. Automated Synthesis for Asynchronous FPGAs. FPGA 2005

-

David Fang, John Teifel, and Rajit Manohar. A High-Performance Asynchronous FPGA: Test Results. FPCCM 2005

-

Rajit Manohar. Reconfigurable Asynchronous Logic. CICC 2006

-

David Fang, et al. A Three-Tier Asynchronous FPGA. VMIC 2006